IBM a anuntat astazi ca a dezvoltat un proces in premiera in industrie cu partenerii Samsung si Globalfoundries pentru a fabrica tranzistori nanofoi din siliciu pentru cipuri de 5 nanometri.

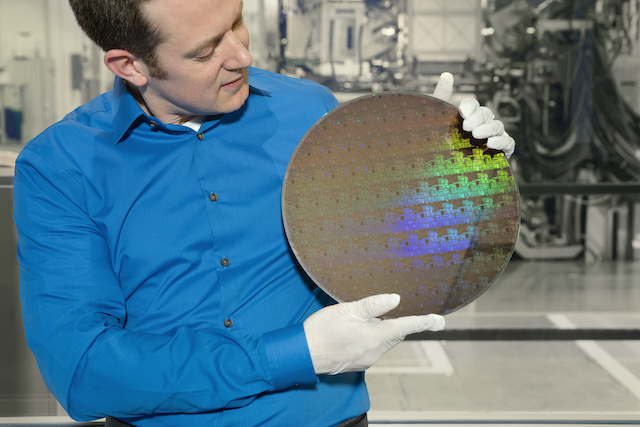

S-a putut face asta in mai putin de doi ani dupa dezvoltarea unui cip de test de 7 nanometri cu 20 de miliarde de tranzistori. Ultimul proces ii permite companiei IBM sa inghesuie 30 de miliarde de tranzistori pe un cip de dimensiunea unei unghii.

IBM are de gand sa ofere detaliile in legatura cu acest proces la 2017 Symposia on VLSI Technology and Circuits Conference din Kyoto, Japonia. Metoda folosita pentru gravarea acestui cip cu 30 de miliarde de tranzistori a fost aceeasi litografie extrema cu ultraviolete (EUV) care a fost folosita pentru cipul de 7 nanometri.

Cu toate acestea, pentru acest proces, designul FinFET de procesor al IBM a fost dat deoparte in favoarea nanofoilor din siliciu. Aceasta schimbare le permite comutatoarelor individuale sa fie ajustate precis, in asa fel incat performanta lor sa poata fi optimizata chiar daca acestea au fost inghesuite in spatiul de dimensiunea unei unghii.

IBM spune ca cresterea de performanta rezultata a cipului cu 30 de miliarde de tranzistori va ajuta la avansarea computing-ului cognitiv, Internetului Lucrurilor si alte intrebuintari bazate pe cloud cu date intensive.

Economisirea de energie ar putea, de asemenea, permite bateriilor din smartphone-uri si alte dispozitive sa aiba o autonomie de trei ori mai lunga decat au acum. Acestea fiind spuse, va trece ceva vreme pana ce aceste dispozitive cu cipuri de 5nm cu 30 de miliarde de tranzistori ale IBM vor ajunge pe piata.

Inca nu am vazut dispozitive cu cipuri de 7 nanometri cu 20 de miliarde de tranzistori, avand in vedere ca se asteapta ca acestea nu vor sosi mai devreme de anul 2018, cel putin. Ceea ce ne spune acest lucru este ca mai avem inca un drum lung de parcurs pana ce performanta dispozitivelor noastre va fi fantastica. Dar stim sigur ca IBM va facilita acest lucru.